# MAS 3528E

# Contents

| Page | Section   | Title                                   |

|------|-----------|-----------------------------------------|

| 5    | 1.        | Introduction                            |

| 5    | 1.1.      | Features                                |

| 6    | 1.2.      | System Application                      |

| 7    | 1.3.      | Application Details                     |

|      |           |                                         |

| 8    | 2.        | Functional Description                  |

| 8    | 2.1.      | Overview                                |

| 8    | 2.2.      | Architecture                            |

| 8    | 2.3.      | DSP Core                                |

| 9    | 2.4.      | Internal Program ROM and Firmware       |

| 9    | 2.5.      | RAM and Registers                       |

| 9    | 2.5.1.    | Program Download Feature                |

| 9    | 2.6.      | Clock Management                        |

| 10   | 2.7.      | Interfaces                              |

| 10   | 2.7.1.    | I <sup>2</sup> C Control Interface      |

| 10   | 2.7.2.    | S/PDIF-Input Interface                  |

| 10   | 2.7.3.    | S/PDIF-Output                           |

| 10   | 2.7.4.    | Serial Input Interface                  |

| 10   | 2.7.4.1.  | Multiline Serial Output                 |

| 10   | 2.7.5.    | Frame Synchronization                   |

| 11   | 2.8.      | Power-Supply Regions                    |

| 11   | 2.9.      | Functional Blocks and Operation         |

| 11   | 2.9.1.    | Power-Up Sequence and Default Operation |

| 12   | 2.9.2.    | Input Switching                         |

| 12   | 2.9.3.    | Standard Selection and Decoding         |

| 12   | 2.9.4.    | Dolby Digital Data Stream               |

| 12   | 2.9.5.    | MPEG Layer-2 Data Stream                |

| 12   | 2.9.6.    | PCM Audio Data                          |

| 12   | 2.9.7.    | Deemphasis                              |

| 12   | 2.9.8.    | Channel Expander                        |

| 13   | 2.9.9.    | Noise Generator                         |

| 13   | 2.9.10.   | Post Processing / Bass Management       |

| 13   | 2.9.10.1. | Downmix                                 |

| 13   | 2.9.10.2. | Digital Volume                          |

| 13   | 2.9.10.3. | Bass Management                         |

| 14   | 2.9.11.   | Output Format Selection                 |

| 15   | 2.9.12.   | DTS / S/PDIF Loop-Through               |

| 15   | 2.9.13.   | Output Sampling Rate                    |

| 15   | 2.10.     | System Interaction                      |

| 15   | 2.10.1.   | Minimum Required Interconnections       |

| 15   | 2.10.2.   | Required Special Modes in the System    |

| 16   | 2.10.3.   | Minimum System Set-Up                   |

|      |           |                                         |

# Contents, continued

| Page | Section  | Title                                                                                                                          |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 17   | 3.       | Control Interface                                                                                                              |

| 17   | 3.1.     | Start-Up Sequence                                                                                                              |

| 17   | 3.2.     | I <sup>2</sup> C Interface Access                                                                                              |

| 17   | 3.2.1.   | General                                                                                                                        |

| 17   | 3.2.2.   | I <sup>2</sup> C Registers and Subaddresses                                                                                    |

| 17   | 3.2.3.   | Conventions for the Command Description                                                                                        |

| 18   | 3.2.4.   | The Internal Fixed Point Number Format                                                                                         |

| 18   | 3.3.     | I <sup>2</sup> C Control Register (Subaddress 6A <sub>hex</sub> )                                                              |

| 18   | 3.4.     | I <sup>2</sup> C Data Register (Subaddresses 68 <sub>hex</sub> and 69 <sub>hex</sub> )<br>and the MAS 3528E DSP-Command Syntax |

| 19   | 3.4.1.   | Run and Freeze                                                                                                                 |

| 20   | 3.4.2.   | Read Register                                                                                                                  |

| 20   | 3.4.3.   | Write Register                                                                                                                 |

| 20   | 3.4.4.   | Read D0 Memory                                                                                                                 |

| 20   | 3.4.5.   | Short Read D0 Memory                                                                                                           |

| 21   | 3.4.6.   | Read D1 Memory                                                                                                                 |

| 21   | 3.4.7.   | Short Read D1 Memory                                                                                                           |

| 21   | 3.4.8.   | Write D0 Memory                                                                                                                |

| 21   | 3.4.9.   | Short Write D0 Memory                                                                                                          |

| 21   | 3.4.10.  | Write D1 Memory                                                                                                                |

| 22   | 3.4.11.  | Short Write D1 Memory                                                                                                          |

| 22   | 3.4.12.  | Default Read                                                                                                                   |

| 23   | 3.5.     | Registers                                                                                                                      |

| 24   | 3.6.     | Special Memory Locations and User Interface                                                                                    |

| 24   | 3.6.1.   | Status Interface for Decoding                                                                                                  |

| 32   | 3.6.2.   | Control Interface for Decoding Operation                                                                                       |

| 40   | 3.6.3.   | Hybrid User Interface Cells                                                                                                    |

|      |          |                                                                                                                                |

| 41   | 4.       | Specifications                                                                                                                 |

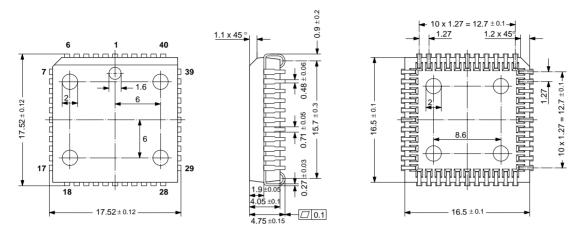

| 41   | 4.1.     | Outline Dimensions                                                                                                             |

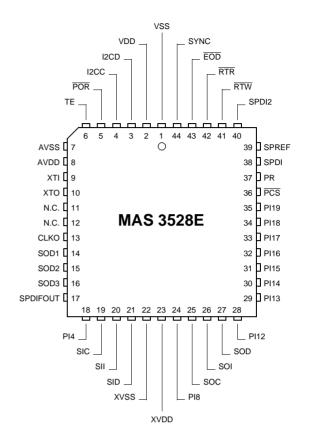

| 41   | 4.2.     | Pin Connections and Short Descriptions                                                                                         |

| 43   | 4.3.     | Pin Descriptions                                                                                                               |

| 43   | 4.3.1.   | Power Supply Pins                                                                                                              |

| 43   | 4.3.2.   | Control Lines                                                                                                                  |

| 43   | 4.3.3.   | Parallel Interface Lines                                                                                                       |

| 43   | 4.3.4.   | Clocking                                                                                                                       |

| 43   | 4.3.5.   | Serial Input Interface                                                                                                         |

| 44   | 4.3.6.   | S/PDIF Input Interface                                                                                                         |

| 44   | 4.3.7.   | S/PDIF Output Interface                                                                                                        |

| 44   | 4.3.8.   | Serial Output Interface                                                                                                        |

| 44   | 4.3.9.   | Miscellaneous                                                                                                                  |

| 44   | 4.4.     | Pin Configuration                                                                                                              |

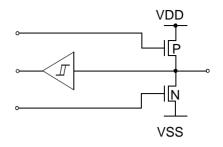

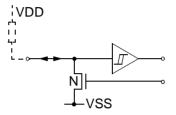

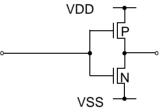

| 45   | 4.5.     | Internal Pin Circuits                                                                                                          |

| 46   | 4.6.     | Electrical Characteristics                                                                                                     |

| 46   | 4.6.1.   | Absolute Maximum Ratings                                                                                                       |

| 47   | 4.6.2.   | Recommended Operating Conditions                                                                                               |

| 47   | 4.6.2.1. | General Recommended Operating Conditions                                                                                       |

#### Contents, continued

| Page | Section  | Title                                                      |

|------|----------|------------------------------------------------------------|

| 47   | 4.6.2.2. | Reference Frequency Generation and Crystal Recommendations |

| 47   | 4.6.2.3. | Input Levels at V <sub>DD</sub> = 4.5 V5.5 V               |

| 48   | 4.6.3.   | Characteristics                                            |

| 48   | 4.6.3.1. | General Characteristics                                    |

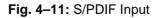

| 49   | 4.6.3.2. | I <sup>2</sup> C Characteristics                           |

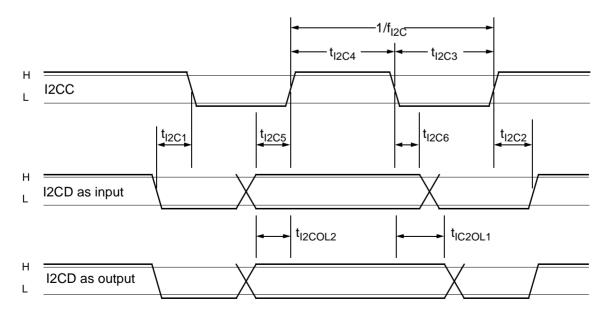

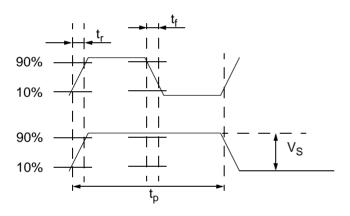

| 50   | 4.6.3.3. | S/PDIF-Bus Input Characteristics                           |

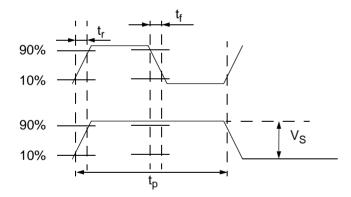

| 51   | 4.6.3.4. | S/PDIF-Bus Output Characteristics                          |

| 52   | 4.6.3.5. | I <sup>2</sup> S Bus Characteristics – Input               |

| 54   | 4.6.3.6. | I <sup>2</sup> S Characteristics – Output                  |

| 55   | 4.6.4.   | Firmware Characteristics                                   |

| 60   | 5.       | Data Sheet History                                         |

#### References

- 1. Digital Audio Compression (AC-3), ATSC Standard, Advances Television Systems Committee, James C. McKinney, Chariman, Dr. Robert Hopkins, Executive Director (Dec. 20, 1995)

- 2. Dolby Licensee Information Manual: Dolby Digital Consumer Decoder, Issue 3, 1999

#### **License Notice**

Dolby-B-NR, Dolby Digital, Dolby Pro Logic, and Dolby Surround Sound are trademarks of Dolby Laboratories.

Supply of this implementation of Dolby Technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use this implementation in any finished end-user or ready-to-use final product. Companies planning to use this implementation in products must obtain a license from Dolby Laboratories Licensing Corporation before designing such products.

# Dolby Digital and MPEG-1 Layer-2 Audio Decoder

#### 1. Introduction

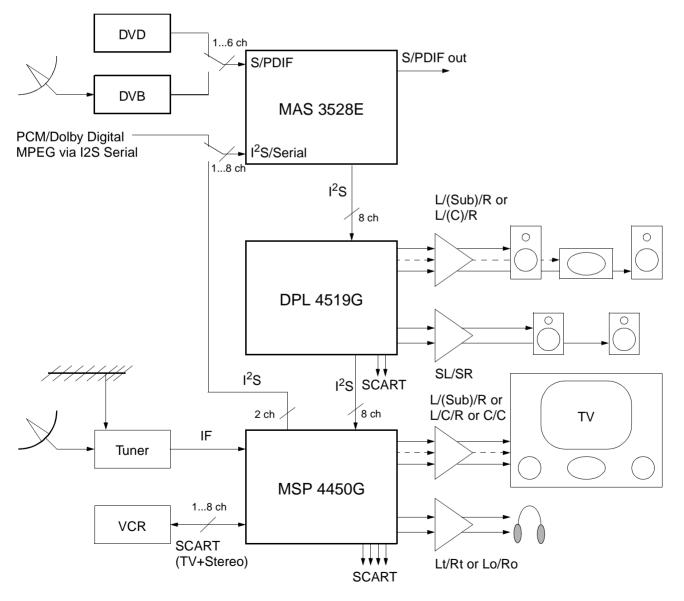

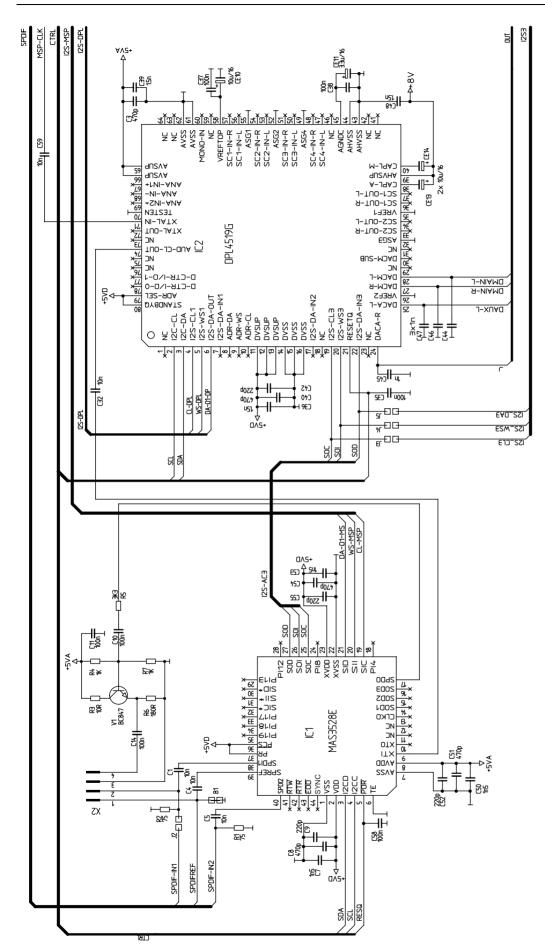

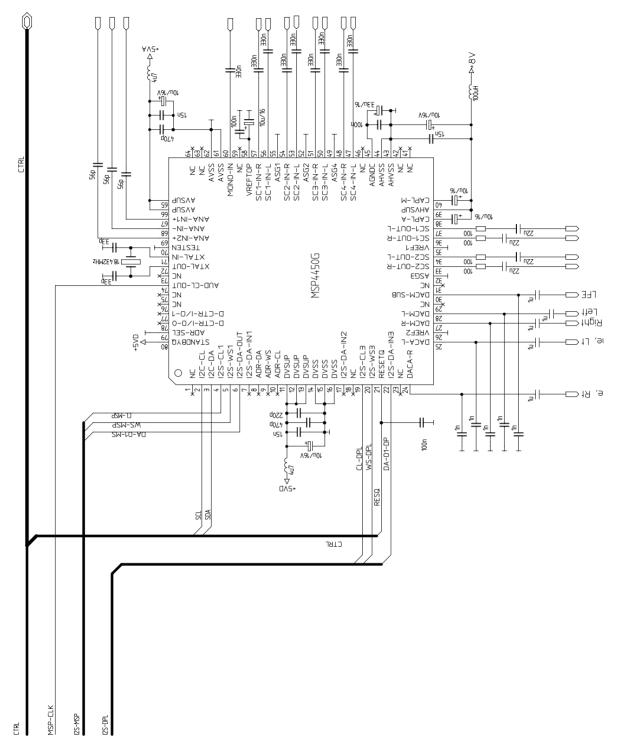

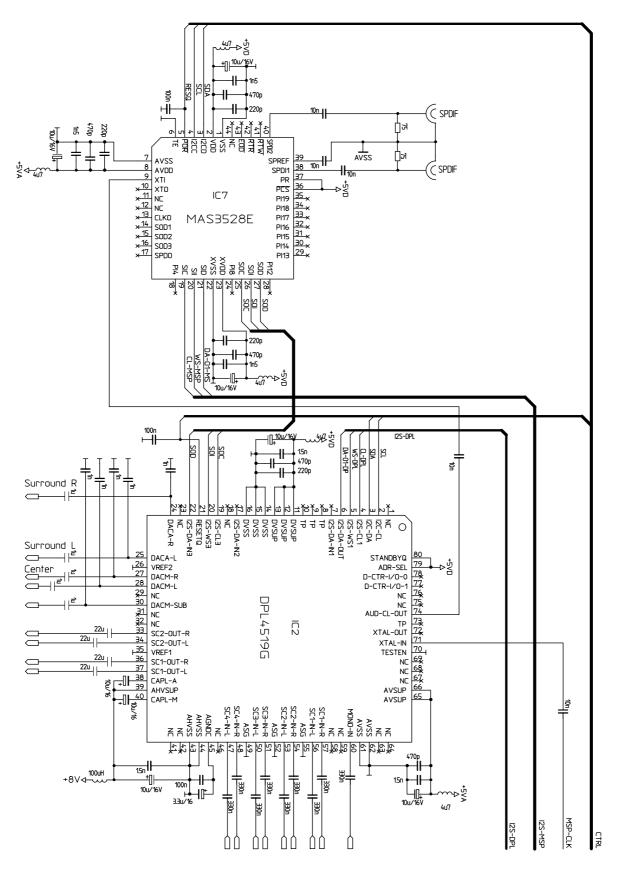

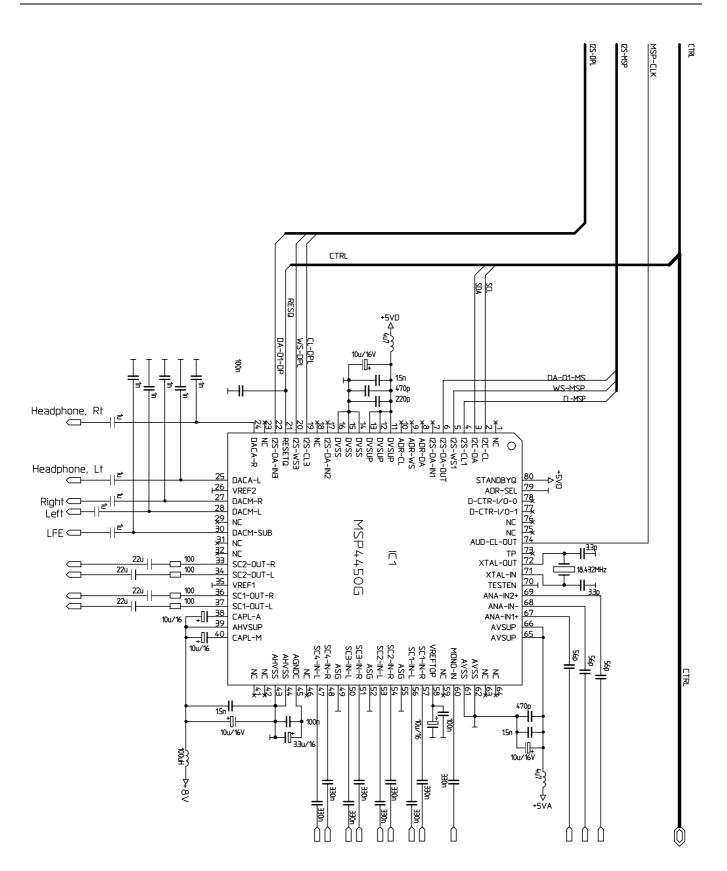

The Micronas MAS 3528E is a single-chip Dolby Digital and MPEG-1 Layer-2 decoder. Together with the Surround Sound Processor DPL 4519G, it acts as a complete implementation of a Dolby Digital consumer decoder. In a television environment, these two integrated circuits are complemented by the Micronas Multistandard Sound Processor MSP 4450G which performs the standard TV sound decoding.

Table 1–1: ICs used for the Dolby Digital System

Solution

| Туре      | Description                                             |

|-----------|---------------------------------------------------------|

| MSP 4450G | Multistandard Sound Processor with 48 kHz processing    |

| DPL 4519G | Sound Processor for digital and analog Surround Systems |

| MAS 3528E | Dolby Digital/MPEG-1 decoder                            |

# 1.1. Features

- S/PDIF, IEC-958, IEC 61937, AES/EBU, EIA-J CP-340 receiver (2 multiplexed inputs)

- Two freely configurable multiplexed serial inputs

- Decoders for 5.1-channel Dolby Digital (AC-3) and MPEG-1 Layer-2

- Handling of PCM input format

- S/PDIF loop-through for DTS (Digital Theater System) and PCM formats

- Optional surround encoding (Lt, Rt) or straight downmixing to two channels (Lo, Ro)

- Multi-channel I<sup>2</sup>S output (four stereo data lines or one 8-channel line)

- Dynamic range compression

- Karaoke downmixing

- Delay for center (0...5 ms)

- Delay for surround (two channels, 0...15 ms)

- Bandpass-shaped/white-noise generator

- Bass management according to Dolby specification (output configuration 0, 1, 2, 3, and DVD)

- I<sup>2</sup>C-control

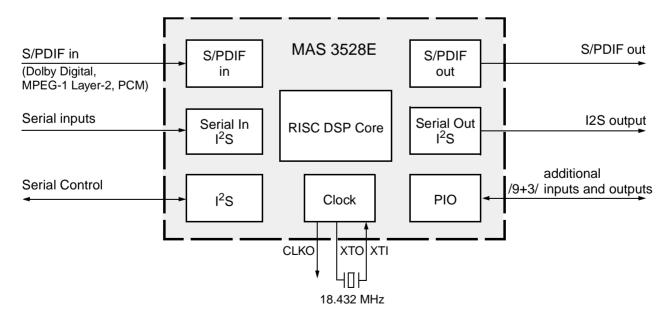

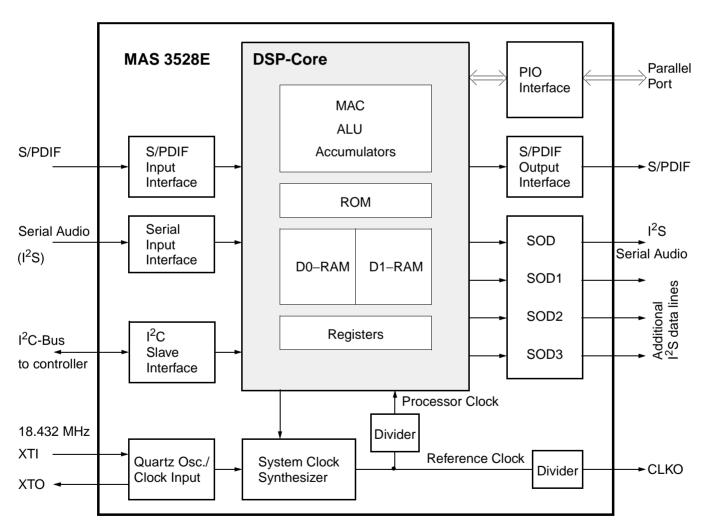

Fig. 1-1: Block diagram MAS 3528E

# 1.2. System Application

The Micronas Dolby Digital system solution consists of three dedicated integrated circuits:

- The MSP 4450G is the interface for all TV-sound and analog input signals. It performs the TV-audio demodulation including analog stereo, NICAM, and Wegener Panda decompression. It has four pairs of audio D/A-converters, two of them including sound control facilities, and one additional subwoofer D/Aconverter.

- The DPL 4519G adds the Dolby Surround Sound features and has three pairs of audio D/A-converters, two of them including sound control facilities, and one additional subwoofer D/A converter.

- The MAS 3528E performs the Dolby Digital or MPEG decoding and has additional functions that are necessary for the Dolby Digital system.

While the MSP 4450G is a stand-alone TV-sound solution, the combination with a DPL 4519G results in a high-end TV with Dolby Pro Logic functionality.

With the addition of the MAS 3528E, the TV provides full Dolby Digital/MPEG-1 capabilities.

A combination of the DPL 4519G with the MAS 3528E is a fully functional Dolby Digital integration for multimedia applications with a total of seven high-quality audio D/A-converters.

Fig. 1-2: Configuration of the Micronas Dolby Digital TV system solution.

# 1.3. Application Details

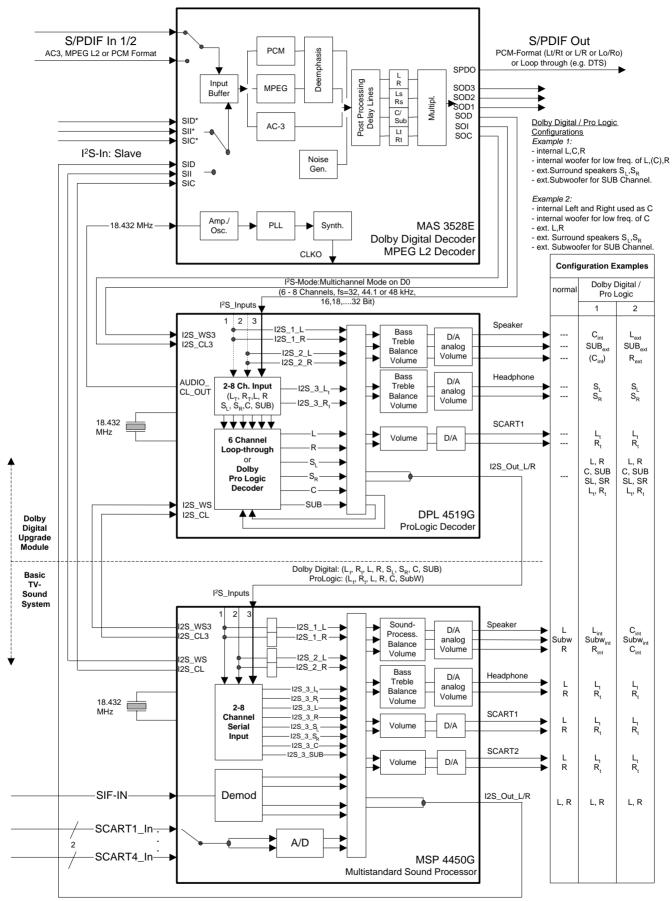

Fig. 1–3: Block diagram of a MAS 3528E in a television environment with all D/A-converters shown.

# 2. Functional Description

# 2.1. Overview

The MAS 3528E is intended for use in high-end consumer audio applications. It receives S/PDIF or serial data streams and decodes the Dolby Digital (AC-3), MPEG or PCM-encoded audio formats.

Due to the automatic format detection, no controller interaction is needed for the standard operation. On the other hand, the controller has full access to all vital information contained in the Dolby Digital bit stream. The choice of different output formats, as defined by Dolby, guarantees good adaption to various listening environments.

# 2.2. Architecture

The hardware of the MAS 3528E consists of a high performance RISC Digital Signal Processor (DSP) and appropriate interfaces. Fig. 2–1 shows a hardware overview of the IC; Fig. 2–2 on page 11 shows the functional aspects.

#### 2.3. DSP Core

The internal processor is a dedicated audio DSP. All data input and output actions are based on a 'non cycle stealing' background DMA that does not cause any computational overhead.

Fig. 2–1: The MAS 3528E architecture

#### 2.4. Internal Program ROM and Firmware

The firmware implemented in the program ROM of the MAS 3528E provides Dolby Digital decoding including the required downmixing, output configurations and delay lines (part of an Implementation of Dolby Digital), MPEG-1 Layer-2 audio data decompression, handling of PCM-encoded audio, and loop-through of DTS-formats received via the S/PDIF-input.

For PCM and MPEG-signals, a deemphasis can be applied to achieve a flat frequency response as required by Dolby Pro Logic decoders.

On power-on, the DSP starts the firmware in an automatic standard detection mode with the S/PDIF-input selected. Therefore, only minimal controlling is necessary. In addition, the I<sup>2</sup>C-interface provides a set of I<sup>2</sup>C instructions that give access to internal DSP-registers and memory areas.

#### 2.5. RAM and Registers

The DSP-core has access to two RAM-banks denoted D0 and D1. All RAM-addresses can be accessed in a 20-bit or a 16-bit mode via  $l^2C$ -bus. For more details, please refer to Section 3.4. on page 18.

For fast access of internal DSP-states, the processor core has an address space of 256 data registers (see Section 3.5. on page 23) which can be accessed via  $I^2C$ -bus.

#### 2.5.1. Program Download Feature

The overall function of the MAS 3528E can be altered by downloading up to 4 kWords of program code into the internal RAM and executing this code instead of the ROM code. While using such alternate program code, no Dolby Digital or MPEG-decoding is possible.

All information concerning the download feature will be distributed together with the download code.

#### 2.6. Clock Management

The MAS 3528E is driven by a single clock at a frequency of 18.432 MHz. The clock may either be provided from an external source to pin XTI or generated with a crystal. At pin XTO, the clock signal is available for other applications. The internal reference clock and processor clock are derived from the 18.432 MHz and synchronized to the audio sample frequency of the decompressed bit stream by a PLL. In case of Dolby Digital decoding, the clock frequency may be selected between a high and a low value by bit[16] in configuration memory cell UIC\_Out\_Clk\_Scale (D0:13DF) – (see Table 3–7 on page 32).

The resulting processor clocks are given in Table 2–1.

At pin CLKO, a clock output can be provided e.g. for additional D/A-converters. The output frequency at CLKO is the reference clock divided by a factor as selected by bits[18:17] in D0:13DF. By default, CLKO is disabled..

Table 2–1: Processor clock frequencies in dependence of bit[16] of UIC\_Out\_Clk\_Scale (D0:13DF).

| Format  | f <sub>s</sub> /kHz Processor Clock/M |             | Clock/MHz   |  |

|---------|---------------------------------------|-------------|-------------|--|

|         |                                       | bit[16] = 0 | bit[16] = 1 |  |

| Dolby   | 48                                    | 61.44       | 73.728      |  |

| Digital | 44.1                                  | 56.448      | 67.7376     |  |

|         | 32                                    | 40.96       | 49.152      |  |

| MPEG,   | 48                                    | 36.864      |             |  |

| PCM     | 44.1                                  | 33.8688     |             |  |

|         | 32                                    | 24.         | .576        |  |

| Table 2–2:         Reference clock frequencies in |

|---------------------------------------------------|

| dependence of bit[16] of                          |

| UIC_Out_Clk_Scale (D0:13DF).                      |

| Format  | f <sub>s</sub> /kHz | /kHz Reference Clock/MH |             |  |

|---------|---------------------|-------------------------|-------------|--|

|         |                     | bit[16] = 0             | bit[16] = 1 |  |

| Dolby   | 48                  | 61.44                   | 73.728      |  |

| Digital | 44.1                | 56.448                  | 67.7376     |  |

|         | 32                  | 40.96                   | 49.152      |  |

| MPEG,   | 48                  | 73.728                  |             |  |

| PCM     | 44.1                | 67.7376                 |             |  |

|         | 32                  | 49                      | .152        |  |

# 2.7. Interfaces

The MAS 3528E uses an  $\mathsf{I}^2\mathsf{C}\text{-interface}$  for control purposes.

Two kinds of digital audio inputs are provided: S/PDIF and a configurable serial input interface. Both interfaces can be used for digital audio data input in the PCM, AC-3 (Dolby Digital), or MPEG format.

For the audio output, a serial multiline interface can be used in different  $I^2S$ -like modes providing up to 8 audio channels. The S/PDIF-output can carry the PCM-audio information or can be used in a loop-through function.

# 2.7.1. I<sup>2</sup>C Control Interface

For controlling and program download purposes, a standard  $I^2C$ -interface is implemented. A detailed description of all functions can be found in Section 3. on page 17

# 2.7.2. S/PDIF-Input Interface

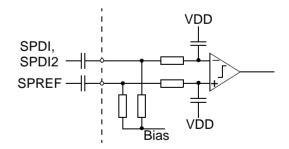

The S/PDIF interface is a one wire serial bus signal. In addition to the signal input pins SPDI/SPDI2, a reference pin SPREF is provided to support balanced signal sources or twisted pair transmission lines. The following features are supported:

- Fast synchronization on input signal (<50 ms)

- Burst-Mode support for Dolby Digital (AC-3) and MPEG-bitstreams

- Locking on 32, 44.1, 48 kHz sample frequencies

- Incoming first 20 channel status bits are mirrored in reg. 56<sub>hex</sub> (see Table 3–5 on page 23)

#### 2.7.3. S/PDIF-Output

At pin SPDIFOUT, the baseband audio is provided as an S/PDIF-signal.

Channel status bits in S/PDIF output (especially copyright, category code, and generation status) can be configured in D0:13EA (see Table 3–7 on page 32).

Alternatively, this output can mirror the unprocessed signal of the S/PDIF-input (Output\_Conf: Register 2e). This loop-through is necessary for DTS (Digital Theater System) signals where no internal decoding action is performed.

#### 2.7.4. Serial Input Interface

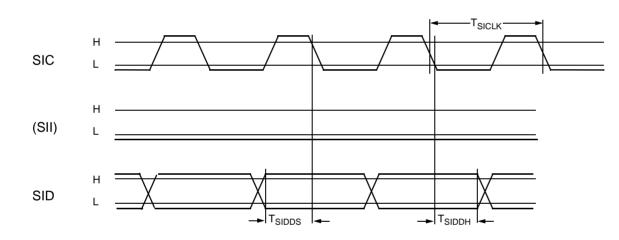

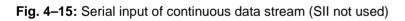

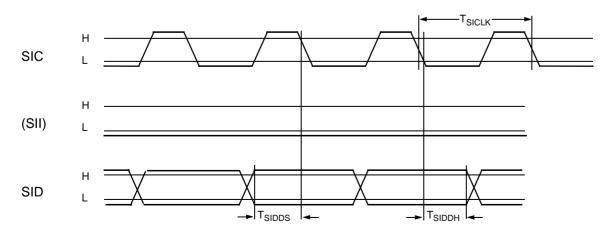

If the serial input interface carries Dolby Digital, MPEG Layer-2, or PCM, the MAS 3528E processes the data. The interface consists of the three pins: SIC, SII, and SID. For MPEG and Dolby Digital decoding operation, the SII pin must always be connected to  $V_{SS}$ , while for PCM-data, the interface acts as an I<sup>2</sup>S-type and SII is used as a word strobe. An example of an input signal format is shown in Fig. 4–17 on page 53. The data values are latched with the falling edge of the SIC signal. It is possible to use a word length of 16 or 32 bits. For controlling details, please refer to memory address D0:13D0 (I/O Control) and D0:13DF (Auxiliary Interface Control) in Table 3–7 on page 32.

If the MPEG or Dolby Digital signal was formatted (e.g. to 8-bit or 16-bit words) by the storing or transportation medium (PC, memory), the serial data must be sent "MSB first" as produced by the encoder.

#### 2.7.4.1. Multiline Serial Output

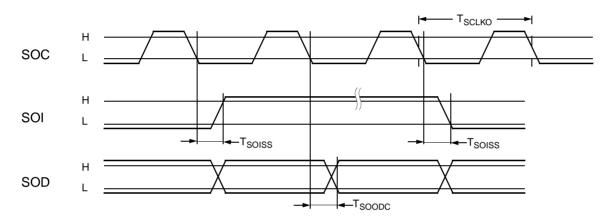

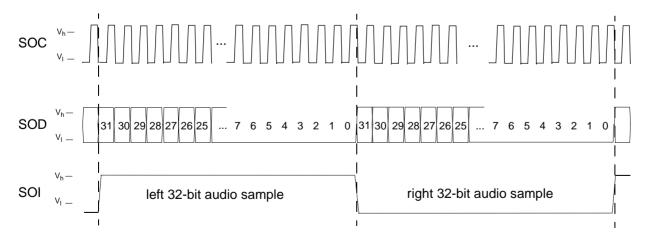

The serial audio output interface of the MAS 3528E is a standard I<sup>2</sup>S-like interface consisting of four data lines SODx, the word strobe SOI, and the clock signal SOC. The output bitstream can either carry eight channels on one line (SOD) or two channels on each of four lines (SOD, SOD1, SOD2, SOD3). Furthermore, it is possible to choose between different interface configurations (with word strobe time offset and/or with inverted SOI-signal). The serial output generates 32 bits per audio sample, but only the first 20 bits will carry valid audio data. The 12 trailing bits are set to zero by default (see Fig. 4–19 on page 54).

The configuration of the output interface is done in D0:13D0 and D0:13DF (see Table 3–7 on page 32).

#### 2.7.5. Frame Synchronization

For microprocessor interrupts, a frame synchronization output pin (SYNC) is provided.

After decoding a valid header, the SYNC pin level changes to High. Most of the status information (UIS cells in Table 3–6 on page 24) is updated now. To generate an edge for the controller, the level changes to Low during processing the next header. After having completed this, the SYNC pin level changes to High again. If the level is Low for more than 1 ms, no decoding is performed. Memory cell UIH\_Last\_error (D0:13FF) provides background information thereof.

#### Notes for Dolby Digital:

After first CRC is done, the SYNC pin level changes to High, all information for a frame is valid, and decoding is performed. The SYNC pin level changes to Low before new status information is written. Please take into account that UIS\_dynrng, UIS\_dynrng2, and UIS\_karaokeflag are valid for the audio block only; the SYNC pin does not signalize their validity.

#### Notes for MPEG:

After processing CRC, the SYNC pin level changes to High, all information for a frame is valid, and decoding is performed. The SYNC pin level changes to Low before evaluating new header information.

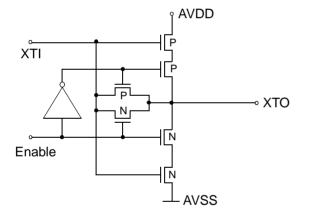

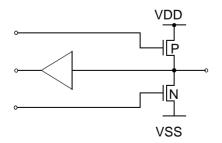

#### 2.8. Power-Supply Regions

The MAS 3528E has three power supply regions. The VDD/VSS-pin pair supplies all digital parts including the DSP-core. The XVDD/XVSS-pin pair is connected to the signal pin output buffers. The AVDD/AVSS-supply is for the clock oscillator, PLL-circuits, and system clock synthesizer.

#### 2.9. Functional Blocks and Operation

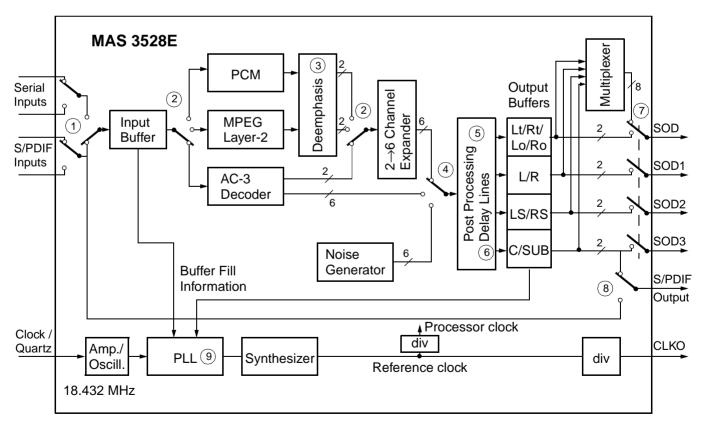

A block diagram of the MAS 3528E functionality is shown in Fig. 2-2.

#### 2.9.1. Power-Up Sequence and Default Operation

After applying the appropriate voltages to the three supply pins and releasing the reset signal, the circuit starts normal operation with the S/PDIF as the expected input and automatic standard recognition (Dolby Digital, MPEG, PCM). No further action is necessary for default operation or DTS loop-through.

A power-on reset can be issued at any time via pin POR.

When the input format is changed (e.g. from Dolby Digital to MPEG), the synchronization is lost and the audio output is muted. The automatic standard recognition then checks the new input format and, after successful recognition, resumes normal operation.

Fig. 2-2: Functionality of the MAS 3528E

# 2.9.2. Input Switching

Both input interfaces, the S/PDIF (default ① in Fig. 2– 2) or the serial input interface, may carry any of the three data formats: Dolby Digital (AC-3), MPEG Layer-2, or PCM. The filling status of the input buffer represents the data rate and therefore controls the system clock. The input interface can be selected in D0:13D0.

The DTS-format can only be received via the S/PDIF-interface for loop-through.

#### 2.9.3. Standard Selection and Decoding

In the default mode, an automatic standard recognition (auto-detection) selects the decoding algorithm according to the data format at the S/PDIF-input. The detected standard is shown in the Global Operating Status (D0:13BB). The standard selection for the  $l^2S$  inputs can be selected manually in D0:13D0 <sup>(2)</sup>.

#### 2.9.4. Dolby Digital Data Stream

The digital input signal can either be an S/PDIF or an  $I^2S$ -source. In the Dolby Digital mode, the IC performs the following tasks:

- Data input with clock synchronization

- S/PDIF-channel selection (one of eight possible)

- Decoding of AC-3 bitstream elements

- Compression control for Dolby Digital signals (Do:13D7...13D9)

- Output mode control

- Dolby Bass Management

- Center and surround delays

- Dynamic compression and level adaption

If the signal source is the S/PDIF-input, the controller may select one of eight content channels depending on availability (D0:13BC). The respective service information is displayed in cell Bit Stream Mode (D0:13A2).

The bit stream elements contain all necessary information required to correctly handle the audio. All elements important for controller actions are displayed in the status memory (see Table 3–6 on page 24).

The MAS 3528E decodes all Dolby Digital formats from 1 to 5.1 audio channels. Accordingly, one to six of the output channels are used for the decoded audio. The output mode is selected in D0:13D6. An additional downmix pair can either be Dolby Surround encoded (Lt, Rt) or plain stereo (Lo, Ro; D0:13DE). If the Dolby Digital input only contains a stereo pair, the controller must recognize this (Dolby Surround Mode D0:13A6) and should activate an external Pro Logic decoder (e.g. in the DPL 4519G).

#### 2.9.5. MPEG Layer-2 Data Stream

In the MPEG mode a valid MPEG-1 Layer-2 data signal is expected. The steps for decoding are

- Clock synchronization to data input

- S/PDIF-channel selection (one of eight possible)

- Side information extraction

- Audio data decompression

- Optional deemphasis

- Digital volume

If the signal source is the S/PDIF-input, the controller may select one of eight content channels depending on availability (D0:13BC).

# 2.9.6. PCM Audio Data

If the PCM-data are received via  $I^2$ S-bus, the MAS 3528E expects a valid word strobe.

The PCM-bitstream does not contain information about the sample rate. Therefore, the controller must get this information from the signal source and set the sample rate in D0:13DB accordingly.

#### 2.9.7. Deemphasis

For the PCM- and MPEG-formats a deemphasis can be applied to the signal ③ (D0:13E0). This is necessary because the possibly following Dolby Pro Logic encoding requires a flat audio frequency response. For MPEG-encoded audio and via S/PDIF transmitted PCM, this block is activated automatically. For proper operation of PCM signals via I<sup>2</sup>S, the controller has to determine whether the PCM signals have been preemphasized or not.

#### 2.9.8. Channel Expander

The outputs of the PCM/MPEG-decoders consist of two channels each; the output of the Dolby Digital decoder may have any number between one and six (5.1) channels. To unify the output format between different modes the audio is always mapped to six channels (.

#### 2.9.9. Noise Generator

A bandpass-shaped or white noise signal can be routed to any combination of the six main output channels ④. The required channel sequence must be done by the controller in D0:13D1.

#### 2.9.10. Post Processing / Bass Management

The implemented post processing functions (5) can be applied to the following audio formats. They are

- Downmixing to Lo/Ro or surround sound encoding to Lt/Rt (D0:13DE) for Dolby Digital multichannel signals

- Mixing and digital filtering for the different Output and Bass configurations according to the Dolby Digital Licensee Information Manual (D0:13Dd5, 13D6, 13DA)

- Digital volume control (D0:13E1...13E8) for all audio formats

- Appropriate delay lines for center and surround channels (D0:13D2...13D4) for Dolby Digital multichannel signals

#### 2.9.10.1. Downmix

For headphone and VCR-recordings, a downmixed output is provided that may be switched from Lt/Rt (surround encoded, default) to Lo/Ro (headphone encoded) (6).

The 6-channel output together with the downmix 6 is routed to the serial data output interface 7.

#### 2.9.10.2. Digital Volume

The digital volume control provided is mainly intended for balancing purposes and initially set to 0 dB. Volume control, output configuration, and delays should be set by the controller according to the actual listening situation.

#### 2.9.10.3. Bass Management

Generally, not all of the five loudspeakers in a Dolby Digital system can reproduce the full audio bandwith. Bass Managment allows redirecting low frequencies to loudspeakers which are capable of reproducing this frequency range. The MAS 3528E supports the following Bass Management modes:

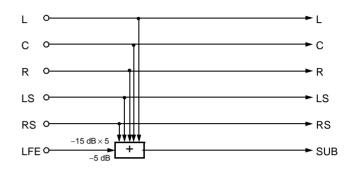

# Bass Management mode 0 (D0:13DA = 8)

Attenuation of -15 dB in the SUB channel should be compensated by a 15 dB gain in the D/A-converter.

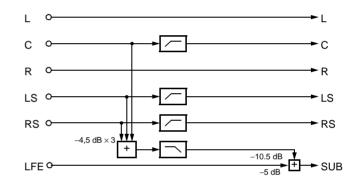

Fig. 2–3: Bass Management configuration 0

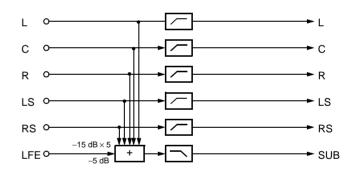

#### Bass Management mode 1 (D0:13DA = 9)

Attenuation of -15 dB in the SUB channel should be compensated by a 15 dB gain in the D/A-converter.

Fig. 2-4: Bass Management configuration 1

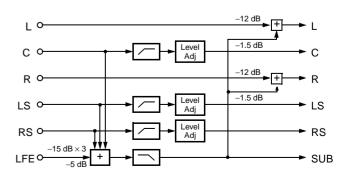

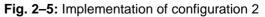

#### Bass Management mode 2 (D0:13DA = A<sub>hex</sub>)

Level adjustment is implemented with -12 db.

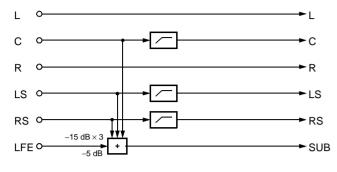

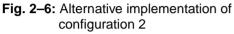

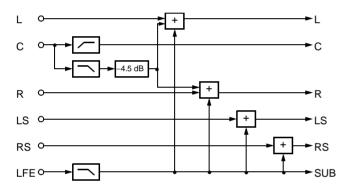

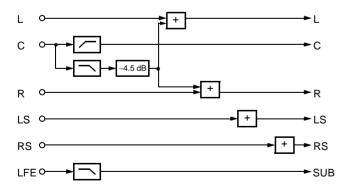

# Bass Management mode 3 (D0:13DA = B<sub>hex</sub>)

# Bass Management mode 4 (D0:13DA = C<sub>hex</sub>)

Fig. 2–7: Implementation of configuration 3

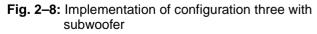

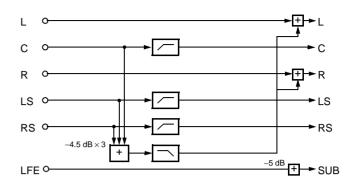

#### Bass Management mode 5 (D0:13DA = D<sub>hex</sub>)

In analog part of SUB should be add a +10 db gain

Bass Management mode 6 (D0:13DA = E<sub>hex</sub>)

Fig. 2–9: Simplified Bass Management for Multichannel Source Products (I)

Bass Management mode 7 (D0:13DA =  $F_{hex}$ )

Fig. 2–10: Simplified Bass Management for Multichannel Source Products )II)

#### 2.9.11. Output Format Selection

The output is an I<sup>2</sup>S-bus format with either eight audio channels on one line (default) or two audio channels on each of four lines (O, D0:13D0). If the 4x2-configuration is selected, the clock and word strobe lines SOC and SOI apply to all four data lines SOD...SOD3. Clock and word strobe signals can be configured to different standards (polarity, delay). The data word length is always 32 bits.

In the 1x8 format, the output data are in the following order:

L, LS, C, Lt/Lo, R, RS, Sub, Rt/Ro.

# 2.9.12.DTS / S/PDIF Loop-Through

An incoming DTS signal (via S/PDIF) will be reflected in GOS\_Type (D0:13BB).

By default, a recognized DTS signal is looped-through. This means that the signal at S/PDIF input is routed to S/PDIF output without processing – regardless of bit 1 in register  $2E_{hex}$ .

This automatism can be disabled by setting bit 12 in register  $2E_{hex}$  to "1". Now, the controller is to choose via bit 1 whether a PCM audio signal is output (in case of a DTS signal the output is muted) or the the input data is looped-through.

#### 2.9.13. Output Sampling Rate

The internally generated system clock is derived from the filling status of the input data buffer by a PLL <sup>(9)</sup>. This clock is synchronous to the original sampling rate and is used throughout the complete data processing. Except in the ambiguous case of PCM-data at the serial audio input where the original sampling rate must be defined (D0:13DB), no controller interaction is needed for clock operation.

The output sampling rate is 32 kHz, 44.1 kHz, or 48 kHz, depending on the source.

Since in the Micronas Dolby Digital TV sound solution all further signal processing is on a rate of 48 kHz, the input stage of the DPL 4519G performs the sample rate conversion if necessary.

#### 2.10.System Interaction

#### 2.10.1. Minimum Required Interconnections

The MAS 3528E requires the following connections for normal operation:

- Power supply with adequate blocking capacitors (VDD, VSS, AVDD, AVSS, XVDD, XVSS)

- Crystal with capacitors or clock input (XTI, XTO)

- I<sup>2</sup>C-bus and reset-line (I2CC, I2CD) and reset line (POR) for controlling

- S/PDIF-input (SPDI/SPDI2, SPREF) or serial/l<sup>2</sup>Sinput (SID, SIC, SII or SID\*, SIC\*, SII\*). In the standard Micronas-solution, the l<sup>2</sup>S-signal comes from the MSP 4450G

- I<sup>2</sup>S-output (SOD, SOC, SOI). In the standard configuration, this signal is fed to the DPL 4519G.

Please refer to Fig. 4–20 on page 56 or to the application kit for details.

#### 2.10.2. Required Special Modes in the System

The MAS 3528E interfaces require no configuration. The I<sup>2</sup>S outputs and inputs of the Dolby Pro Logic IC DPL 4519G and the MSP 4450G, however, must be configured to send/accept the 8-channel multiplexed digital PCM-data stream.

The DPL 4519G may generate up to seven analog signals (three pairs plus subwoofer). Further audio signals can be forwarded to the MSP 4450G for D/A-conversion.

Dolby Pro Logic encoded audio originating from the MSP 4450G (TV-sound) must be routed through the MAS 3528E to the DPL 4519G for further processing.

# 2.10.3. Minimum System Set-Up

The following  $I^2C$ -command sequence is necessary for the DPL 4519G:

- I<sup>2</sup>C-controlled reset

- Write MODUS Register (set I<sup>2</sup>S-input to slave mode)

- Write I2S\_CONFIG (multi sample mode, 32 bits, clock to 8\*32 bits)

- Set I2S3 Resorting Matrix to "left/right eight MAS 3528E". The signal pairs are now in the following order: Lt/Rt, L/R, SL/SR, C/Sub

- Select first I<sup>2</sup>S3-input pair as source for I<sup>2</sup>S Output (because of 8\*32-bit mode all 4\*2 channels will be looped through to the MSP 4450G) and set to transparent stereo

- Select one input pair as source for Loudspeaker Output (numbers 7...10 mean first...fourth pair)

- Select one input pair as source for Aux Output (numbers 7...10 mean first...fourth pair)

- Set volume control for Loudspeaker Output

- Set volume control for Aux Output

If a Multistandard Sound Processor is present in the system, similar set-up commands are required. For further details, please refer to the DPL 4519G or the MSP 4450G data sheets.

If both devices are used on the same I<sup>2</sup>C-bus, the device addresses must be set to different values by hardware means.

The D/A-conversion of audio signals may be freely appointed between the DPL 4519G and the MSP 4450G. For an example, please refer to Table 2–4.

| Device                                                                                                                                                               | DPL 4519G                       |                             |                                | MSP 4450G                       |                             |                                |                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|--------------------------------|---------------------------------|-----------------------------|--------------------------------|--------------------------------|

| $\begin{array}{l} \text{Register} \rightarrow \\ \text{Signal Pair} \downarrow \end{array}$                                                                          | Loudsp.<br>00 08 <sub>hex</sub> | Aux<br>00 09 <sub>hex</sub> | SCART1<br>00 0A <sub>hex</sub> | Loudsp.<br>00 08 <sub>hex</sub> | Aux<br>00 09 <sub>hex</sub> | SCART1<br>00 0A <sub>hex</sub> | SCART2<br>00 41 <sub>hex</sub> |

| Lt/Rt (Lo/Ro)                                                                                                                                                        | 07 20 <sub>hex</sub>            | 07 20 <sub>hex</sub>        | 07 20 <sub>hex</sub>           | 07 20 <sub>hex</sub>            | 07 20 <sub>hex</sub>        | 07 20 <sub>hex</sub>           | 07 20 <sub>hex</sub>           |

| L/R                                                                                                                                                                  | 08 20 <sub>hex</sub>            | 08 20 <sub>hex</sub>        | 08 20 <sub>hex</sub>           | 08 20 <sub>hex</sub>            | 08 20 <sub>hex</sub>        | 08 20 <sub>hex</sub>           | 08 20 <sub>hex</sub>           |

| SL/SR                                                                                                                                                                | 09 20 <sub>hex</sub>            | 09 20 <sub>hex</sub>        | 09 20 <sub>hex</sub>           | 09 20 <sub>hex</sub>            | 09 20 <sub>hex</sub>        | 09 20 <sub>hex</sub>           | 09 20 <sub>hex</sub>           |

| C/Sub                                                                                                                                                                | 0A 20 <sub>hex</sub> 1)         | 0A 20 <sub>hex</sub> 1)     | 0A 20 <sub>hex</sub> 1)        | 0A 20 <sub>hex</sub> 1)         | 0A 20 <sub>hex</sub> 1)     | 0A 20 <sub>hex</sub> 1)        | 0A 20 <sub>hex</sub> 1)        |

| <sup>1)</sup> Use 0A 20 <sub>hex</sub> for C/Sub output, 0A 00 <sub>hex</sub> for Center signal on both outputs, 0A 10 <sub>hex</sub> for Sub signal on both outputs |                                 |                             |                                |                                 |                             |                                |                                |

**Table 2–3:** Output configuration matrix. All registers are at  $l^2$ C-subaddress  $12_{hex}$  of the respective device. Note that only one code per register applies.

**Table 2–4:** Example: In the DPL 4519G use both loudspeaker output channels for center, the auxiliary output for surround, the SCART1 output for Lt/Rt. In the MSP 4450G use the loudspeaker output for L/R, both auxiliary output channels for Sub and the SCART1 output for an additional Lt/Rt-signal.

| Device                                                                                      | ce DPL 4519G                    |                             |                                 | MSP 4450G                       |                             |                                |                                |

|---------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|---------------------------------|---------------------------------|-----------------------------|--------------------------------|--------------------------------|

| $\begin{array}{l} \text{Register} \rightarrow \\ \text{Signal Pair} \downarrow \end{array}$ | Loudsp.<br>00 08 <sub>hex</sub> | Aux<br>00 09 <sub>hex</sub> | SCART1<br>00 0Aa <sub>hex</sub> | Loudsp.<br>00 08 <sub>hex</sub> | Aux<br>00 09 <sub>hex</sub> | SCART1<br>00 0A <sub>hex</sub> | SCART2<br>00 41 <sub>hex</sub> |

| Lt/Rt (Lo/Ro)                                                                               |                                 |                             | 07 20 <sub>hex</sub>            |                                 |                             | 07 20 <sub>hex</sub>           |                                |

| L/R                                                                                         |                                 |                             |                                 | 08 20 <sub>hex</sub>            |                             |                                |                                |

| SL/SR                                                                                       |                                 | 09 20 <sub>hex</sub>        |                                 |                                 |                             |                                |                                |

| C/Sub                                                                                       | 0A 00 <sub>hex</sub>            |                             |                                 |                                 | 0A 10 <sub>hex</sub>        |                                |                                |

# 3. Control Interface

#### 3.1. Start-Up Sequence

After power-up and a reset (see Section 3.3. on page 18), the IC is in its default state (see Table 3–7 on page 32). The controller has to initialize all memory cells for which a non-default setting is necessary.

# 3.2. I<sup>2</sup>C Interface Access

#### 3.2.1. General

Control communication with the MAS 3528E is done via an  $I^2C$  slave interface. The device addresses are  $3A_{hex}$  (write) and  $3B_{hex}$  (read) as shown in Table 3–1.

I<sup>2</sup>C clock synchronization is used to slow down the interface if required.

Table 3–1: I<sup>2</sup>C device address

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | W/R |

|----|----|----|----|----|----|----|-----|

| 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0/1 |

#### 3.2.2. I<sup>2</sup>C Registers and Subaddresses

The interface uses one level of subaddresses. The MAS 3528E interface has 3 subaddresses allocated for the corresponding  $I^2C$ -registers.

The address  $6A_{hex}$  is used for basic control, i.e. reset and task select. The other addresses are used for data transfer from/to the MAS 3528E.

The I<sup>2</sup>C-control and data registers of the MAS 3528E are 16 bits wide, the MSB is denoted as bit [15]. Transmissions via I<sup>2</sup>C-bus have to take place in 16-bit words (two byte transfers, MSB sent first); thus for each register access two 8-bit data words must be sent/received via I<sup>2</sup>C-bus.

Table 3-2: Subaddresses

| Sub-<br>address   | l <sup>2</sup> C-<br>Register | Function                                           |

|-------------------|-------------------------------|----------------------------------------------------|

| 68 <sub>hex</sub> | data                          | Controller writes to<br>MAS 3528E data register    |

| 69 <sub>hex</sub> | data                          | Controller reads from<br>MAS 3528E data register   |

| 6A <sub>hex</sub> | control                       | Controller writes to<br>MAS 3528E control register |

# 3.2.3. Conventions for the Command Description

The description of the various controller commands uses the following formalism:

- Abbreviations used in the following descriptions:

- a address

- d data value

- n count value

- o offset value

- r register number

- x don't care

- A data value is split into 4-bit nibbles which are numbered zero-bound.

- Data values in nibbles are always shown in hexadecimal notation.

- A hexadecimal 20-bit number **d** is written, e.g. as  $\mathbf{d} = 17C63_{hex}$ , its five nibbles are  $d0 = 3_{hex}$ ,  $d1 = 6_{hex}$ ,  $d2 = C_{hex}$ ,  $d3 = 7_{hex}$ , and  $d4 = 1_{hex}$ .

- Variables used in the following descriptions:

| dev_write  | 3A <sub>hex</sub> | device write           |

|------------|-------------------|------------------------|

| dev_read   | 3B <sub>hex</sub> | device read            |

| data_write | 68 <sub>hex</sub> | data register write    |

| data_read  | 69 <sub>hex</sub> | data register read     |

| control    | 6A <sub>hex</sub> | control register write |

- Bus signals

- S Start

- P Stop

- A ACK = Acknowledge

- N NAK = Not acknowledge

- Symbols in the telegram examples

- < Start Condition

- > Stop Condition

- dd data byte

- xx ignore

All telegram numbers are hexadecimal, data originating from the MAS 3528E are shown in gray. Example:

| <3A 68 | dd dd>     | write data to DSP  |

|--------|------------|--------------------|

| <3A 69 | <3B dd dd> | read data from DSP |

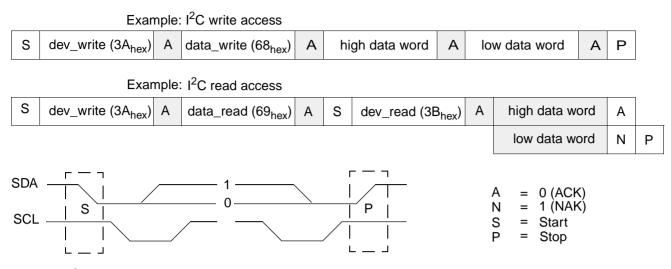

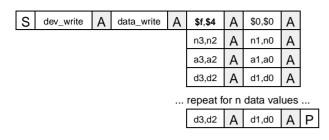

Fig. 3–1 shows  $I^2C$  bus protocols for read and write operations of the interface; the read operation requires an extra start condition and repetition of the chip address with the read command ( $3B_{hex}$ ). Fields with signals/data originating from the MAS 3528E are marked by a gray background. Note that in some cases, the data reading process must be concluded by a NAK condition.

Fig. 3–1: I<sup>2</sup>C bus protocol for the MAS 3528E (MSB first; data must be stable while clock is high)

#### 3.2.4. The Internal Fixed Point Number Format

In the following sections, two number representations are used: The fixed point notation 'v' and the 2's complement number notation 'r'.

The conversion between the two forms of notation is easily done (see the following equations).

| r = v*524288.0+0.5; (−1.0 ≤ v < 1.0) | (EQ 1) |

|--------------------------------------|--------|

|--------------------------------------|--------|

v = r/524288.0; (-524288 < r < 524287) (EQ 2)

#### 3.3. I<sup>2</sup>C Control Register (Subaddress 6A<sub>hex</sub>)

| S dev_write A control A d3,d2 A d1,d0 A P |

|-------------------------------------------|

|-------------------------------------------|

The  $I^2C$  control register is a write-only register. Its main purpose is the software reset of the MAS 3528E. The software reset is done by writing a 16-bit word to the MAS 3528E with bit 8 set. The four least significant bits are reserved for task selection. The task selection is only useful in combination with download software. In standard Dolby Digital/MPEG-decoding, these bits must always be set to 0.

Table 3-3: Control register bit assignment1)

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| x  | x  | x  | x  | x  | x  | x  | R  | 0  | 0  | 0  | 0  | Т3 | T2 | T1 | т0 |

1) x = don't care, R = reset, T3...T0 0 task selection

# 3.4. I<sup>2</sup>C Data Register (Subaddresses 68<sub>hex</sub> and 69<sub>hex</sub>) and the MAS 3528E DSP-Command Syntax

The DSP-core of the MAS 3528E has two RAM-banks denoted D0 and D1. The word size is 20 bits. All RAM-addresses can be accessed in a 20-bit or a 16-bit mode via I<sup>2</sup>C-bus. For fast access of internal DSP-states, the processor core also has an address space of 256 data registers. All register and RAM-addresses are given in hexadecimal notation.

The control of the DSP in the MAS 3528E is done via the I<sup>2</sup>C data register by using a special command syntax. These commands allow the controller to access the DSP-registers and RAM-cells and thus monitor internal states, set the parameters for the DSP-firmware, control the hardware, and even provide a download of alternative software modules.

The DSP-commands consist of a "Code" which is sent to  $I^2C$ -data register together with additional parameters.

| S | dev_write | А | data_write | А | Code, | А | , | А |  |

|---|-----------|---|------------|---|-------|---|---|---|--|

The MAS 3528E firmware scans the I<sup>2</sup>C interface periodically and checks for pending or new commands. The commands are then executed by the DSP during its normal operation without any loss or interruption of the incoming data or outgoing audio data stream. However, due to some time critical firmware parts, a certain latency time for the response has to be expected. The theoretical worst case response time does not exceed 4 ms. However, the typical response time is less than 0.5 ms. Table 3–4 on page 19 shows the basic controller commands that are available by the MAS 3528E.

ī

| Code<br>(hex) | Command            | Function                                                                                                                 |

|---------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0 3           | Run                | Start execution of an internal program. <i>Run</i> with start address 0 <sub>hex</sub> means freeze the operating system |

| А             | Read from register | Controller reads an internal register of the MAS 3528E.                                                                  |

| В             | Write to register  | Controller writes an internal register of the MAS 3528E.                                                                 |

| С             | Read D0 memory     | Controller reads a block of the DSP memory.                                                                              |

| D             | Read D1 memory     | Controller reads a block of the DSP memory.                                                                              |

| E             | Write D0 memory    | Controller writes a block of the DSP memory.                                                                             |

| F             | Write D1 memory    | Controller writes a block of the DSP memory.                                                                             |

| Table 3-4: Basic controller | command codes |

|-----------------------------|---------------|

|-----------------------------|---------------|

Table 3–4 gives an overview of the different commands which the DSP-core may receive. The "Code" is always the first data nibble transmitted after the "data\_write" byte. A second auxiliary code nibble is used for the short memory access commands.

Because of the 16-bit width of the  $I^2C$ -data register, all actions always transmit telegrams with multiples of 16 data bits.

#### 3.4.1. Run and Freeze

| S | dev write | Δ | data_write | Δ | <b>a3</b> a2 | Δ | a1 a0 | Δ | Р |

|---|-----------|---|------------|---|--------------|---|-------|---|---|

| 3 | uev_write | A | uala_white | А | as,az        | А | a1,a0 | A | Г |

The *Run* command causes the start of a program part at address  $\mathbf{a} = (a3,a2,a1,a0)$ . Since nibble a3 is also the command code (see Table 3–4), it is restricted to values between 0 and 3.

If the start address is  $1000_{hex} \le a < 1FFF_{hex}$  and the respective RAM area has been configured as program RAM (see Table 3–5 on page 23), the MAS 3528E continues execution with a custom program already downloaded to this area (see Section 2.5.1. on page 9).

Example 1: Start program execution at address 345<sub>hex</sub>:

<3A 68 03 45>

Example 2: Start execution of a downloaded code at address  $1000_{hex}$ :

<3A 68 10 00>

*Freeze* is a special run command with start address 0. It suspends all normal program execution. The operating system will enter an idle loop so that all registers and memory cells can be watched. This state is useful for operations like downloading code or contents of memory cells because the internal program cannot overwrite these values. This freezing will be required if alternative software is downloaded into the internal RAM of the MAS 3528E (see Section 2.5.1. on page 9).

#### Freeze has the following I<sup>2</sup>C protocol:

<3A 68 00 00>

The entry point of the default software will be accessed automatically. Thus issuing a *Run* or *Freeze* command is only necessary for starting downloaded software or special program modules which are not part of the standard set.

# 3.4.2. Read Register

| 1) se                 | 1) send command |                                         |     |           |  |    |   |     |          |   |     |     |   |   |

|-----------------------|-----------------|-----------------------------------------|-----|-----------|--|----|---|-----|----------|---|-----|-----|---|---|

| S                     | dev_write       | dev_write A data_write A \$a,r1 A r0,\$ |     |           |  |    |   |     | \$0      | А | Ρ   |     |   |   |

| 2) get register value |                 |                                         |     |           |  |    |   |     |          |   |     |     |   |   |

| S                     | dev_write       | Α                                       | dat | data_read |  |    | S | dev | dev_read |   |     |     |   |   |

|                       |                 | x,                                      | x   | A x,o     |  | d4 | А | d3, | d2       | А | d1, | ,d0 | Ν | Ρ |

The MAS 3528E has an address space of 256 DSPregisters. Some of the registers ( $\mathbf{r} = r1,r0$  in the figure above) are direct control inputs for various hardware blocks, others control the internal program flow. In Section 3.5. on page 23, the registers of interest with respect to the Dolby Digital/MPEG-decoding firmware are described in detail. In contrast to memory cells, registers cannot be accessed as a block but must always be addressed individually.

Example:

Read the content of register (2E<sub>hex</sub>):

| <3A | 68 | A2 E0>           | define register |

|-----|----|------------------|-----------------|

| <3A | 69 | <3B xx xd dd dd> | and read        |

#### 3.4.3. Write Register

| S | dev_write | А | data_write | A \$b,r1 |       | Α | r0,d4 | А |   |

|---|-----------|---|------------|----------|-------|---|-------|---|---|

|   |           |   |            |          | d3,d2 | Α | d1,d0 | Α | Ρ |

The controller writes the 20-bit value  $(\mathbf{d} = d4, d3, d2, d1, d0)$  into the MAS 3528E register  $(\mathbf{r} = r1, r0)$ . A list of registers is given in Section 3.5. on page 23

Example: Disable automatic S/PDIF loop-through for DTS by writing the value  $1000_{hex}$  into the register with the number  $2E_{hex}$ :

<3A 68 B2 E0 10 00>

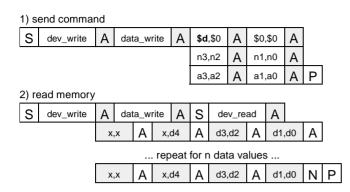

#### 3.4.4. Read D0 Memory

The MAS 3528E has 2 memory areas called D0 and D1. Both areas have different read and write commands.

1) send command S dev write А data write А **\$c**,\$0 А \$0,\$0 А n3,n2 A n1,n0 А a3,a2 a1,a0 А Р A 2) read memory S dev\_write А data\_write А S dev read А d3,d2 d1,d0 x,x А x,d4 А А А ... repeat for n data values ... А x,d4 A d3,d2 A d1,d0 N P x.x

The *Read D0 Memory* command gives the controller access to all 20 bits of D0-memory cells of the MAS 3528E. The telegram to read three words starting at location  $D0:100_{hex}$  is

<3A 68 C0 00 00 03 01 00> <3A 69 <3B xx xd dd dd xx xd dd dd xx xd dd dd>

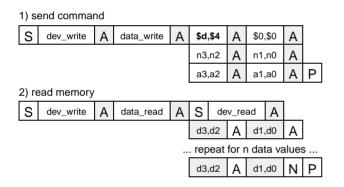

#### 3.4.5. Short Read D0 Memory

Because most cells in the Dolby Digital user interface are only 16 bits wide, it is faster and more convenient to access the memory locations with a special 16-bit mode for reading:

1) send command

| S              | dev_write                | А | data_write | Α | \$c,     | \$4 | А    | \$0   | ,\$0  | А |   |  |

|----------------|--------------------------|---|------------|---|----------|-----|------|-------|-------|---|---|--|

|                |                          |   |            |   | n3,      | n2  | A n1 |       | n1,n0 |   |   |  |

|                |                          |   |            |   | a3,      | a2  | А    | a1,a0 |       | А | Ρ |  |

| 2) read memory |                          |   |            |   |          |     |      |       |       |   |   |  |

| S              | dev_write                | А | data_read  | А | S dev_re |     | v_re | ad    | А     |   |   |  |

|                |                          |   |            |   | d3,d2 A  |     |      | d1,d0 |       | А |   |  |

|                | repeat for n data values |   |            |   |          |     |      |       |       |   |   |  |

|                |                          |   |            |   | d3,      | d2  | А    | d1    | ,d0   | Ν | Ρ |  |

This command is similar to the normal 20-bit read command and uses the same command codes  $C_{hex}$ , however, this nibble is followed by a  $4_{hex}$  rather than a  $0_{hex}$ .

# 3.4.6. Read D1 Memory

The *Read D1 Memory* command is provided to get information from D1 memory cells of the MAS 3528E.

# 3.4.7. Short Read D1 Memory

The Short Read D1 Memory command works similarly to the Read D1 Memory command but with the code  $D_{hex}$  followed by a  $4_{hex}$ .

Example: Read 16 bits of D1:123 has the following I<sup>2</sup>C protocol:

| <3A 68 | D4 00      | read 16 bits from D1 |

|--------|------------|----------------------|

|        | 00 01      | one word to be read  |

|        | 01 23>     | start address        |

| <3A 69 | <3B dd dd> | start reading        |

#### 3.4.8. Write D0 Memory

|   |           |   |            |   |                 |      |         |     | - |

|---|-----------|---|------------|---|-----------------|------|---------|-----|---|

| S | dev_write | А | data_write | А | <b>\$e</b> ,\$0 | А    | \$0,\$0 | А   |   |

|   |           |   |            |   | n3,n2           | А    | n1,n0   | А   |   |

|   |           |   |            |   | a3,a2           | А    | a1,a0   | А   |   |

|   |           |   |            |   | 0,0             | А    | 0,d4    | А   |   |

|   |           |   |            |   | d3,d2           | А    | d1,d0   | А   |   |

|   |           |   |            |   | repeat f        | or n | data va | ues |   |

|   |           |   |            |   | 0,0             | А    | 0,d4    | А   |   |

|   |           |   |            |   | d3,d2           | Α    | d1,d0   | А   | Ρ |

With the *Write D0 Memory* command n 20-bit memory cells in D0 can be initialized with new data.

Example: Write  $80234_{hex}$  to D0:FFB<sub>hex</sub> has the following I<sup>2</sup>C protocol:

| <3A | 68 | ΕO | 00  | write D0 memory                  |

|-----|----|----|-----|----------------------------------|

|     |    | 00 | 01  | 1 word to write                  |

|     |    | 0F | Fb  | start address FFB <sub>hex</sub> |

|     |    | 00 | 08  | value = $80234_{hex}$            |

|     |    | 02 | 34> | TOX .                            |

#### 3.4.9. Short Write D0 Memory

| S | dev_write | А | data_write | А | \$e,\$4  | А    | \$0,\$0  | А   |   |

|---|-----------|---|------------|---|----------|------|----------|-----|---|

|   |           |   |            |   | n3,n2    | А    | n1,n0    | А   |   |

|   |           |   |            |   | a3,a2    | А    | a1,a0    | А   |   |

|   |           |   |            |   | d3,d2    | А    | d1,d0    | А   |   |

|   |           |   |            |   | repeat f | or n | data val | ues |   |

|   |           |   |            |   | d3,d2    | А    | d1,d0    | А   | Ρ |

For faster access, only the lower 16 bits of each memory cell are accessed. The four MSBs of the cell are cleared. The code combination is  $E4_{hex}$ .

#### 3.4.10.Write D1 Memory

|   |           |   |            | - |                 | -    |          |     |   |

|---|-----------|---|------------|---|-----------------|------|----------|-----|---|

| S | dev_write | А | data_write | А | <b>\$f</b> ,\$0 | А    | \$0,\$0  | А   |   |

|   |           |   |            |   | n3,n2           | А    | n1,n0    | А   |   |

|   |           |   |            |   | a3,a2           | А    | a1,a0    | А   |   |

|   |           |   |            |   | 0,0             | А    | 0,d4     | А   |   |

|   |           |   |            |   | d3,d2           | А    | d1,d0    | А   |   |

|   |           |   |            |   | repeat f        | or n | data val | ues |   |

|   |           |   |            |   | 0,0             | А    | 0,d4     | А   |   |

|   |           |   |            |   | d3,d2           | Α    | d1,d0    | А   | Ρ |

For further details, see the Write D0 Memory command.

# 3.4.11.Short Write D1 Memory

Only the 16 lower bits of each memory cell are written, the upper four bits are cleared.

#### 3.4.12. Default Read

The *Default Read* command is the fastest way to get information from the MAS 3528E. Executing the *Default Read* in a polling loop can be used to detect a special state during decoding.

| S | dev_write | А | data_read | А | S | device_read |     | А  |   |   |  |

|---|-----------|---|-----------|---|---|-------------|-----|----|---|---|--|

|   |           |   |           |   |   | d3,d2       | d1, | d0 | Ν | Ρ |  |

The *Default Read* command immediately returns the lower 16 bit content of a specific RAM location as defined by the pointer D0:FFB<sub>hex</sub>. The pointer must be loaded before the first *Default Read* action occurs. If the MSB of the pointer is set, it points to a memory location in D1 rather than to one in D0.

Example: For watching D1:123, the pointer D0:FFB must be loaded with 8123<sub>hex</sub>:

| <3A | 68 | ΕO  | 00 | write to D0 memory       |

|-----|----|-----|----|--------------------------|

|     | 00 | 01  |    | one word to write        |

|     | 0F | Fb  |    | start address FFB        |

|     | 00 | 08  |    | value = 8 <sub>hex</sub> |

|     | 01 | 23> | >  | 0123 <sub>hex</sub>      |

Now the *Default Read* commands can be issued as often as desired:

| <3A 69 <3B        | Default Read command              |

|-------------------|-----------------------------------|

| dd dd>            | 16 bit content of the             |

|                   | address as defined by the pointer |

| <3A 69 <3B dd dd> | and do it again                   |

#### 3.5. Registers

In Table 3–5, the internal registers that are useful for controlling the MAS 3528E are listed. They are accessible by Read/Write Register  $I^2C$  commands (see Section 3.4.2. and Section 3.4.3. on page 20).

# Note: Registers not given in this table must not be written.

# Table 3–5: Command Register Table

| Register<br>Address<br>(hex) | R/W | Function  |                                                                                                                                                                                              | Default<br>(hex) | Name        |

|------------------------------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|

| 2E                           | R/W | Loop-thro | ugh and Sync Pin Controlling                                                                                                                                                                 | 00000            | Output_Conf |

|                              |     | bit[12]   | <ol> <li>automatic active loop-through if DTS is<br/>recognized or the input format at<br/>S/PDIF_in cannot be determined<br/>(default)</li> <li>bit[1] controls<br/>loop-through</li> </ol> |                  |             |

|                              |     | bit[11:2] | reserved: do not change!                                                                                                                                                                     |                  |             |

|                              |     | bit[1]    | <ul><li>0: normal operation</li><li>1: connect SPDI_in to SPDIF OUT<br/>(loop-through)</li></ul>                                                                                             |                  |             |

|                              |     | bit[0]    | sync bit (will be automatically detected and set by internal software)                                                                                                                       |                  |             |

| 56                           | R   | Incoming  | S/PDIF Channel Status Bits                                                                                                                                                                   |                  | SPIOCS      |

|                              |     | bit[19:0] | mirrors first 20 channel status bits                                                                                                                                                         |                  |             |

#### 3.6. Special Memory Locations and User Interface

Operation of the DSP and the interfaces can be observed and controlled via the memory locations of the user interface. These memory cells are located at the high end of the D0-RAM.

Status cells are written by the DSP and read by the controller, configuration cells are written by the controller and read by the DSP, hybrid cells can be written and read by either side.

#### Note: Memory addresses not given in this table must not be accessed.

#### 3.6.1. Status Interface for Decoding

The following table contains the memory locations of the firmware status information. Addresses are hexadecimal, memory cell content is binary when written without indicator and hexadecimal when written with a hex-suffix.

| Memory<br>Address<br>(hex) | Function Mode                                                                                                                                                                                                                                                                                                                                                                                         | Name      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| D0:13A0                    | AC-3 Sample Rate Codes (fscod)Dolby Digital(Table 5.1 of ATSC Spec. A/52)                                                                                                                                                                                                                                                                                                                             | UIS_FSCOD |

|                            | bit[1:0] 00 48 kHz<br>01 44.1 kHz<br>10 32 kHz<br>11 not detected (default)                                                                                                                                                                                                                                                                                                                           |           |

|                            | AC-3 sample rate as included in the bit stream.                                                                                                                                                                                                                                                                                                                                                       |           |

| D0:13A1                    | Bit Stream Identification (bsid)Dolby Digital(Section 5.4.2.1 of ATSC Spec. A/52)                                                                                                                                                                                                                                                                                                                     | UIS_BSID  |

|                            | bit[4:0] 00 <sub>hex</sub> 1f <sub>hex</sub> current bsid value                                                                                                                                                                                                                                                                                                                                       |           |

|                            | Bit streams that have a bsid higher than the decoder's version number may be incompatible. In this case, the decoding is inhibited. The version number for the implemented firmware is 8.                                                                                                                                                                                                             |           |

| D0:13A2                    | Bit Stream Mode (bsmod)Dolby Digital(Table 5.2 of ATSC Spec. A/52)                                                                                                                                                                                                                                                                                                                                    | UIS_BSMOD |

|                            | bit[2:0]000main audio service: complete main (CM)001main audio service: music and effects (ME)010associated service: visually impaired (VI)011associated service: hearing impaired (HI)100associated service: dialogue (D)101associated service: commentary (C)110associated service: emergency (E)111acmod = 001, associated service: voice over (VO)111acmod = 010-111, main audio service: karaoke |           |

|                            | This information is valid after selecting (D0:13D0) an available (D0:13BC) channel (data stream) from the S/PDIF-input. Prior to this, the bsmod can be directly derived from the PC-preambles of the S/PDIF-data (D0:13BD13C4)                                                                                                                                                                       |           |

| Memory<br>Address<br>(hex) | Function                      |                                              |                                                                                                                              |                                                                                               | Mode          | Name        |

|----------------------------|-------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|-------------|

| D0:13A3                    |                               | <b>g Mode (acmod)</b><br>ATSC Spec. A/52)    |                                                                                                                              |                                                                                               | Dolby Digital | UIS_ACMOD   |

|                            | 0<br>0<br>1<br>1<br>1<br>1    | 110 2/2<br>111 3/2                           | bsmod != '111'<br>Ch1, Ch2<br>C<br>L, R<br>L, C, R<br>L, C, R<br>L, C, R, S<br>L, C, R, S<br>L, R, SL, SR<br>L, C, R, SL, SR | Voice Over (\<br>L, R<br>L, M, R<br>L, R, V1<br>L, M, R, V1<br>L, R, V1, V2<br>L, M, R, V1, V | /O)           |             |

|                            | For user inform               | mation: indicates                            | the applied main                                                                                                             | channel.                                                                                      |               |             |

| D0:13A4                    |                               | <b>evel (cmixlev)</b><br>ATSC Spec. A/52)    | 1                                                                                                                            |                                                                                               | Dolby Digital | UIS_CLEV    |

|                            | 0                             | 01 0.595<br>10 0.500<br>11 reser<br>nomin    | 7 (-3.0 dB)<br>5 (-4.5 dB)<br>0 (-6.0 dB)<br>ved (-6.0 dB),<br>nal downmix leve<br>ect to left and righ                      |                                                                                               | h             |             |

|                            | Used in the in                | nternal algorithm.                           |                                                                                                                              |                                                                                               |               |             |

| D0:13A5                    |                               | <b>x Level (surmixle</b><br>ATSC Spec. A/52) |                                                                                                                              |                                                                                               | Dolby Digital | UIS_SLEV    |

|                            | 0                             | 01 0.500<br>10 0<br>11 reser                 | ′ (–3.0 dB)<br>) (–6.0 dB)<br>ved (–6.0 dB),<br>nal downmix leve                                                             | l of surround (                                                                               | channels      |             |

|                            | Used in the in                | nternal algorithm.                           |                                                                                                                              |                                                                                               |               |             |

| D0:13A6                    |                               | und Mode (dsurn<br>ATSC Spec. A/52)          |                                                                                                                              |                                                                                               | Dolby Digital | UIS_DSURMOD |

|                            | 0                             | 01 not D<br>10 Dolby                         | dicated<br>olby Surround en<br>v Surround encoo<br>ved (not indicate                                                         | ded                                                                                           |               |             |